97.5804 Assignment #4: Design Synthesis

NOTE: When watching all the videos below, ensure that you play them full screen so that everything is readable (you can do this by clicking on the YouTube icon in the lower righthand corner to watch in YouTube, which allows you to view the videos at the full resolution of 1920x1080). Also, if you try to watch them on a mobile device through 3G, YouTube downgrades the resolution and they look horrible. Probably you'll want to bring headphones to the lab in order to hear the audio.

NOTE: The name of the server has changed since I made these videos. So whenever I type or say "macopeland" replace that with "boothroyd". This is very important!

Part 1: Introduction and Set-up

NOTE: The name of the server has changed since I made these videos. So whenever I type or say "macopeland" replace that with "boothroyd". This is very important!

Part 1: Introduction and Set-up

In this assignment, we are going to synthesize an IIR filter. We're not going to write the code for this filter, so don't panic.

There is an interesting web site called OPENCORES.ORG, which you should all visit and examine. At OPENCORES, you will find opensource verilog and VHDL code. We're going to use some code from OPENCORES in this assignment. I've copied the necessary files from OPENCORES and packaged them up with some other files that you will need for this assignment.

You should log in and open a terminal window, and then enter these commands:

% cd

% tar --no-same-owner -xvf /home/maceacla/elec5804a4.tar

% cd Training/ELEC5804/assignment04

% ls -Ra

That does a recursive listing of the directories. You can also use the file browser in Linux to look around at the directory structure so that you have a good idea of what is in the .tar file.

You should read the file in the DOCs directory. Use the file browser to navigate to this file and then view it using a PDF viewer:

~/Training/ELEC5804/assignment04/biquad/DOCs/biquad.pdf

You should also review the contents of the verilog files in the HDLs directory. Each of these files defines a portion of the biquad filter. The primary file is bqmain.v which implements the filter using the modules contained in the other files.

There are a few set-up files contained in the .tar file and after the untarring step from above they should appear in the assignment04 directory and they are discussed in the videos below.

Several of these files define the target libraries used to synthesize the design. Examine these files carefully and try to find the target files mentioned. For reference, the files are as follows:

wcells_synopsys_dc.setup.tcl file targets the wcells library without using DesignWare components.

wcells_plus_DW_synopsys_dc.setup.tcl file targets the wcells library and uses DesignWare components.

gpdk90_synopsys_dc.setup.tcl file targets the gpdk90 library without using DesignWare components.

gpdk90_plus_DW_synopsys_dc.setup.tcl file targets the gpdk90 library and uses DesignWare components.

gtech_synopsys_dc.setup.tcl file targets the generic library supplied with Synopsys Design Compiler, without using DesignWare components.

gtech_plus_DW_synopsys_dc.setup.tcl file targets the generic library supplied with Synopsys Design Compiler, and uses DesignWare components.

As discussed in the videos, the wcells library is from an old design kit, and it contains information for a standard cell library implemented in 0.35μm CMOS technology. The gpdk90 library is the library for the standard cells in our 90nm CMOS technology design kit (AMSKIT).

The following video shows how to set-up your directory for assignment #4.

Part 2: Analyzing and Elaborating

In this section, we'll load the verilog files in the Synopsys Design Vision tool. This tool lets us examine verilog and VHDL code schematically. Type the following:

% cd ~/Training/ELEC5804/assignment04

% source assignment_4_setup

% design_vision -64bit

After a few moments, the "Synopsys Design Vision" window will appear.

Starting up the Synopsys tool is covered in the next video:

Next, you have to load in the verilog files that are in the HDLs directory. Here is the procedure:

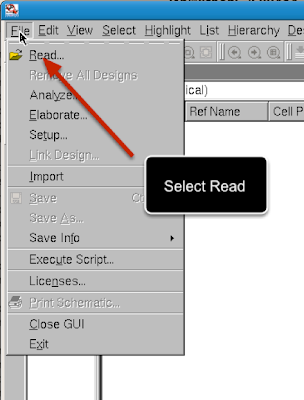

Go to File→Read, navigate to biquad/HDLs, and select bqmain.v and then press the Open button.

Once bqmain.v is loaded, the design_vision window will appear as below. Note that there are some warnings near the bottom of the window. These warnings arise because bqmain.v refers to functions not appearing in the loaded file.

At this point design_vision hasn’t fully analyzed the biquad filter code. Press the schematic generation button as shown in the next figure, and you’ll see that design_vision has analyzed the interconnections between the various verilog modules, but there is no clear structure otherwise shown in the generated schematic.

Next we’ll get design_vision to load the rest of the code and analyze it.

Do this by going to File→Analyze, which brings up another window called "Analyze File". Use the file browser in this window to select all the files in the HDLs directory (hold in the control key to select multiple files). Click OK, and allow design_vision to create a “WORK” directory.

The next step is to "Elaborate" the verilog code you've loaded. All this means is that Synopsys Design Analyzer is going to examine the code and convert it to an internal representation used by the tool. The advantage of doing this is that once elaborated, you can look at your code graphically.

Go to File→Elaborate. The "Elaborate Design" window pops up. You should change the library to “WORK” and the design to bqmain(verilog). Then click OK. Then click on the schematic generator button again and your window should resemble the following screen shot.

This looks a lot like a circuit, right? Zoom in until you see the pin labels clearly.

You should be able to review the verilog module code, the generated schematic, and the PDF file in the DOCs directory to arrive at a reasonable description of each of the above pins and the two blocks "coefio" and "biquad".

In the schematic window you can click on one of the blocks (e.g. biquadi) and then select from the menus Schematic→Move Down to descend into the block. You’ll see an impressive schematic that represents the verilog code for that module. Zoom in and take a look at the various components (use the “z” key). Make note of the component names. If you click on a component and type “Control-r” a pop-up window appears with more information about the component. Try this for some components.

To get back up in the hierarchy of the design, select Schematic→Move Up.

You should zoom in on various portions of this schematic to get a feeling for the complexity of the design. This schematic is a visual representation of the biquad.v verilog code. Nothing has been synthesized yet. For example, find the block corresponding to multb10.v (hint: use the hierarchy browser to the left of the design_vision window). Descend into this block and see if there is a schematic representation.

Part 3: Preparation for Synthesis

Go back up to the top level of the hierarchy. In order to synthesize our design, we need to define a couple of things, mainly clocks and capacitive loads. We'll do this just so we can get a synthesis run to work - it's not necessarily going to be the best implementation.

First, define some loading for the outputs. Drag a window around the "ack_o", "dat_o", and "y" pins to select them. Then go to Attributes→Operating Environment→Load. Fill in 0.2 for the capacitive load (that's in pF). Click Ok.

Next, click on "clk_i" and then go to Attributes→Specify Clock. In the pop-up form, change the Period to 25 (that's a 40MHz clock). Fill in the rest of the form as shown below and then Click OK.

Next, click on "dspclk" and then go to Attributes→Specify Clock. In the pop-up form, change the Period to 12.5 (that's a 80MHz clock). Fill in the rest of the form as shown below and then Click OK.

Next, we can use a typed-in command to set the clock uncertainty. As shown in the screen shot below, enter “set_clock_uncertainty 0.25 -from CLK_0 -to CLK_1. Note that if you happened to name your clocks differently in the preceding steps, the names should be used in this command instead.

That's enough to get a synthesis run to work.

Part 4: Synthesis

Go back up to the top level of the hierarchy (click on the up-arrow icon to the left of the window a few times).

Select the bqmain icon. Again in the command entry area, type “uniquify” (without the quotation marks). This will create copies of all modules that are called more than once in the verilog code.

Select the bqmain icon again. In the command entry area, type “compile” (without the quotation marks).

The compile should take less than 5 minutes.

Once the compile is finished, descend into the bqmain module. Explore the different blocks, and note the difference in the appearance of the generated schematic. You should see that the multipliers that were previously undefined now contain complex circuitry to perform the multiplication. Synopsys has taken the verilog code, mapped the functions to the operations available in the targeted library or libraries, and then generated a schematic based on these library functions.

Neat, eh?!

EXAMPLE VIDEOS:

The following videos provide examples and further information about synthesis and using design_vision.

Loading files, setting constraints, and compiling:

Compiling to an alternative library:

Compiling to reduce layout area:

Generating reports:

Checking path timing:

Finding synthesized components in the target library:

Information about libraries:

Part 5: Assignment Requirements

No formal write-up is required for this assignment. Instead, you will receive a “Google Form” by email. Perform simulations, use design_vision, and read the documentation as required to fill in this form.

Be smart about running simulations synthesis. If you think ahead, you can use the supplied .tcl scripts and basically run each required simulation synthesis with just a couple of mouse clicks. There should be no need to repeatedly enter the constraints, etc.

The following information is no longer needed since Google Forms now accepts image uploads. I'll leave it here for posterity.

Note that some of the questions ask for screen shots of your work. Please use imgur.com to upload your screenshots, and provide the URLs as answers to the questions in the forms. The video below explains how to do this.

Note that some of the questions ask for screen shots of your work. Please use imgur.com to upload your screenshots, and provide the URLs as answers to the questions in the forms. The video below explains how to do this.

OTHER REFERENCES:

If you find any good reference material useful for undertaking this assignment, let me know and I'll add it into this section. For now, I found the following helpful reading: